웨이퍼와 재료공학

1. 웨이퍼 기판(Wafer Substrate)

반도체 공정의 시작은 웨이퍼(반도체 기판) 소재의 선택과 특성이 전체 공정에 영향을 주므로 매우 중요

* 주요 재료

- 실리콘(Si) : 가장 일반적인 반도체 기판. 다이아몬드 구조로 전기적 특성이 우수하고 대량 생산이 가능함.

- 실리콘 온 인슐레이터(SOI, Silicon-On-Insulator) : 절연층이 있어 기생 커패시턴스(Parasitic Capacitance) 를 줄이고, 저전력 고속 트랜지스터 제작 가능.

- GaN(질화갈륨), SiC(탄화규소) : 전력 반도체(Power Semiconductor) 및 RF(고주파) 소자에 사용. 고온·고전압에서도 성능 유지 가능.

- Ge(게르마늄), III-V 화합물(예: GaAs, InP) : 고속 디지털 및 광소자에 사용. 전자 이동도(Electron Mobility) 가 높아 고성능 트랜지스터 제작 가능.

* 실리콘의 결정학적 장점

- 다이아몬드 구조 (Diamond Cubic Lattice)

- 실리콘은 FCC(Face-Centered Cubic) 구조를 기반으로 한 다이아몬드 구조 를 형성함.

- 이 구조는 결함 밀도가 낮고, 전자 이동도가 균일하여 회로 동작 안정성이 우수 함.

- 결정 성장(크리스탈 성장)이 용이

- 실리콘은 Czochralski (CZ) 방법 으로 단결정을 쉽게 성장시킬 수 있음.

- 불순물이 상대적으로 적고, 웨이퍼의 대량 생산이 가능함.

- 산화 공정이 가능함

- 실리콘은 자연적으로 SiO₂(이산화규소) 를 형성하는 특성이 있어, 트랜지스터의 게이트 절연막(Gate Dielectric) 으로 활용 가능.

- GaAs(갈륨비소) 같은 III-V 화합물 반도체는 안정적인 산화막 형성이 어렵기 때문에, 실리콘이 더욱 선호됨.

- 열적 안정성이 높음

- 실리콘의 융점(1414°C) 이 높아 반도체 제조 공정에서 열처리에 유리함.

- 열팽창계수(CTE, Coefficient of Thermal Expansion)가 비교적 낮아 기판의 변형이 적음.

* 반도체 웨이퍼의 결정 방향과 그 영향

실리콘 웨이퍼는 특정한 밀러 지수(Miller Index) 방향 으로 절단됨.

- (100) 방향: 주로 CMOS 공정에서 사용됨. 산화막 형성이 균일하고, 식각(Etching)이 용이함.

- (110) 방향: FinFET 공정에서 사용됨. 전자 이동도(Electron Mobility) 가 향상됨.

- (111) 방향: 화합물 반도체(GaAs, SiC)에서 사용됨. 결정 구조가 치밀하고, 기계적 강도가 높음.

* 결정 방향에 따른 에칭 속도 차이

- 실리콘은 이방성 식각(Anisotropic Etching) 특성을 가지며, 결정 방향에 따라 식각 속도가 다름.

- 예를 들어, KOH(Kalium Hydroxide) 용액으로 식각 시 (100) 방향보다 (111) 방향이 훨씬 느리게 식각됨.

- 이 특성을 이용해 MEMS 공정에서 기계적 스트레스를 제어하는 구조 설계 를 함.

* 열응력(Thermal Stress)과 웨이퍼 휨(Wafer Bow)

- 반도체 공정에서는 여러 박막을 웨이퍼 위에 증착하는데, 이때 각 층의 열팽창계수(CTE) 차이 로 인해 응력이 발생함.

- 예를 들어, Si(2.6 × 10⁻⁶ /K)와 SiO₂(0.5 × 10⁻⁶ /K) 의 열팽창계수가 다르므로 산화막이 형성될 때 인장 응력(Tensile Stress) 또는 압축 응력(Compressive Stress) 이 발생함.

*미세화에 따른 Stress Engineering

7nm 이하 노드에서는 미세 패턴이 기계적 스트레스에 매우 민감해짐.

Si₃N₄(질화규소) 스트레스 라이너(Stress Liner) 를 사용해 PMOS와 NMOS의 이동도를 다르게 조절하는 기술 이 적용됨.

- NMOS: 인장 응력(Tensile Stress) 을 걸어 전자 이동도를 증가.

- PMOS: 압축 응력(Compressive Stress) 을 걸어 홀(Hole) 이동도를 증가.

2. 산화 공정에서의 치환 반응과 재료공학적 영향

웨이퍼의 산화 공정에서 Si → SiO₂ 변환 과정 은 화학적 치환 반응을 동반

* 산화 과정에서 일어나는 반응

- 건식 산화 (Dry Oxidation)

- Si + O₂ → SiO₂

- 고밀도의 절연층을 형성하지만 성장 속도가 느림.

- 습식 산화 (Wet Oxidation)

- Si + 2H₂O → SiO₂ + 2H₂

- 수증기(H₂O)가 참여하여 산화 속도가 빠르지만, 산화막의 밀도가 낮아질 수 있음.

* 치환 반응과 원자 확산

- 산화가 진행될 때, 산소(O₂) 원자 또는 OH⁻ 라디칼이 실리콘 결정 격자로 확산 하면서 Si 원자가 SiO₂로 치환됨.

- 실리콘 원자는 산소와 결합하여 산화막을 형성하지만, 이 과정에서 실리콘의 부피가 증가 하게 됨.

- SiO₂는 Si보다 약 2.2배 부피가 커서, 내압(Compressive Stress)이 발생 함.

- 이 응력은 웨이퍼에 슬립 결함(Slip Defect)이나 산화 스트레스 결함(Stress-Induced Defects) 을 유발할 수 있음.

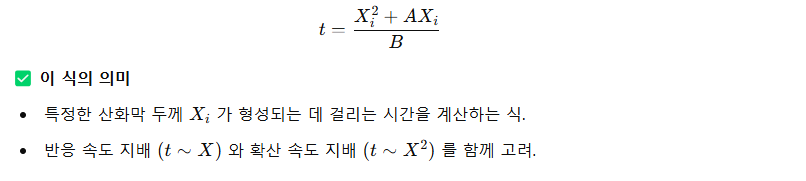

Deal-Grove 모델

(1) 산화막 형성 속도

(2) 산화막 두께(X)

(3) 시간(t)과 산화막 두께(X)의 관계

예)

질문 : (100) Si를 대기압에서 1시간 산화 1373K에서 열처리 시 건식, 습식의 산화막 두께 구하기

문제: 건조 산화를 이용하여 1200K에서 2000Å(0.2μm)의 산화막을 성장하는데 필요한 시간은?

* SiO₂ 열산화(High-Temperature Oxidation)

- 1200°C, 습식 산화(Wet Oxidation) → 확산 지배, 빠른 산화 속도.

- 900°C, 건식 산화(Dry Oxidation) → 반응 지배, 균일한 얇은 산화막 형성.

* 미세 공정에서의 저온 산화(Low-Temperature Oxidation)

- FinFET, GAA 소자에서는 얇은 절연막이 필요하므로 건식 산화가 선호됨.

- Deal-Grove 모델을 활용하여, 700~900°C에서 균일한 산화막을 형성 함.

3. 반도체에서 결함의 영향

웨이퍼에서 발생하는 주요 결함

- 공공(Vacancy) 결함

- 결정 구조에서 원자가 빠져나간 자리로, 반도체에서 확산(Diffusion) 을 촉진하는 역할을 함.

- 공공 농도를 제어하지 않으면 도핑된 원소들이 비정상적으로 확산(Dopant Diffusion)하여 임계 전압(Vth) 변동 이 생길 수 있음.

- 전위(Dislocation)

- 전위는 결정 내에서 원자 배열이 불완전한 선(Line) 결함이며, 웨이퍼의 기계적 강도를 약화 시킴.

- 특히, GaN이나 SiC 같은 화합물 반도체에서는 전위 밀도가 높아 전류 누설 문제(Leakage Current)가 심각해질 수 있음.

- 이를 해결하기 위해 ELOG(Epitaxial Lateral Overgrowth) 같은 성장 기법 이 사용됨.

- 슬립(Slip) 결함

- 고온 열처리 중 발생하는 전단 변형(Shear Deformation)으로, 소자의 활성 영역에서 결함이 생기면 소자의 신뢰성이 낮아짐.

- 슬립 결함을 방지하기 위해 웨이퍼를 서서히 가열하고 천천히 냉각하는 어닐링(Annealing) 공정 이 적용됨.

* 박막과 웨이퍼 계면에서 발생하는 반응

- 박막이 웨이퍼에 증착될 때, 두 물질 간의 화학 반응 및 원자 확산 이 일어날 수 있음.

- 대표적인 예로 Cu(구리)와 Si(실리콘) 간 반응 이 있는데, Cu는 Si 내부로 쉽게 확산되어 pn 접합을 손상 시킬 수 있음.

- 이를 방지하기 위해 Ta, TaN 배리어 메탈(Barrier Metal)을 증착 하여 Cu 확산을 차단함.

*Fick’s Law를 이용한 확산 제어

확산(Diffusion)은 반도체 공정에서 도핑(Doping), 배선 확산(Interconnect Diffusion), 불순물 제어 등에 중요한 역할을 함.

확산 거리는 Fick’s Second Law 로 표현됨:

- D (확산 계수) 는 온도에 따라 달라지며, Arrhenius 관계 를 따름:

여기서 E 는 활성화 에너지, k는 볼츠만 상수, T는 절대온도.

- 이를 활용하면, 특정 온도에서 도핑 확산 깊이를 예측할 수 있으며, 고온 공정에서 불필요한 확산(Excessive Diffusion)을 최소화하는 전략 을 세울 수 있음.

* 결함이 반도체 성능에 미치는 영향

- 공공과 슬립 결함은 누설 전류(Leakage Current)를 증가 시켜 반도체 소자의 성능을 저하시킬 수 있음.

- 전기적 불균일성(Electrical Non-uniformity) 증가

- 결정 결함이 많으면 소자의 동작 특성이 칩마다 다르게 나타남.

- 기계적 신뢰성(Mechanical Reliability) 저하

- 웨이퍼의 강도가 감소하여, 제조 공정 중 크랙이 발생할 가능성이 높아짐.